## Parallelismo del bus

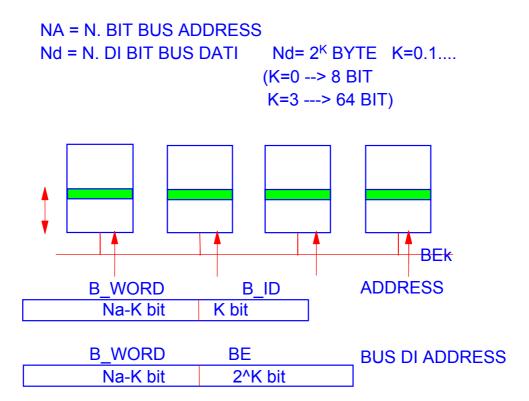

- •Dato un microprocessore con parallelismo del bus dati a Nd bit, con Nd =  $2^K * 8$ , assumiamo che nel suo bus degli indirizzi i primi K bit  $A_{0+}A_{K-1}$  siano sostituiti da  $2^K$  segnali  $BE_i$ . (es.  $16=2^{1*}8$ , K=1. 1 bit per la codifica dei banchi)

- •I segnali BE<sub>i</sub> sono la versione "decodificata" degli Ai: ciascuno di essi si attiva individualmente quando il corrispondente banco di memoria deve essere abilitato.

- •La dimensione in byte della memoria è arbitraria (ad esempio, 4 GB, cioè NA = 32).

## Memoria a 16 bit

Organizzazione della memoria: parallelismo a 16 bit

I bit BE0\* e BE1\* corrispondono esattamente a A0\* e BHE\* dell'8086

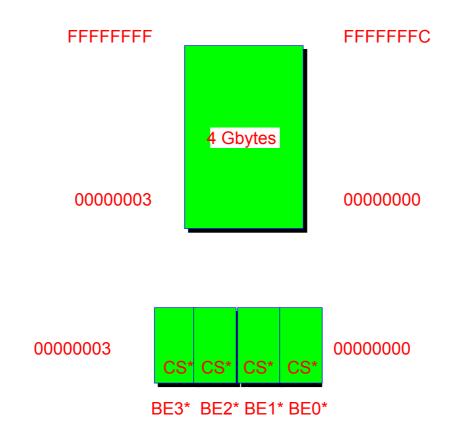

## Memoria a 32 bit

Organizzazione della memoria: parallelismo a 32 bit (esempio, bus del 486).

I bit BE0\*, BE1\*, BE2\*, BE3\* abilitano il corrispondente banco in funzione dell'istruzione eseguita dal processore (in genere sono lecite solo configurazioni di byte contigui in memoria).

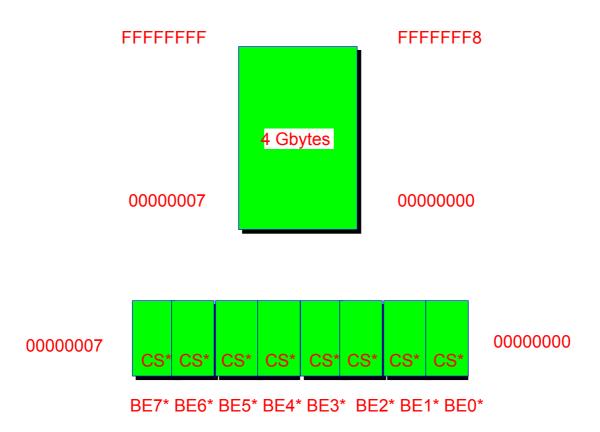

## Memoria a 64 bit

Organizzazione della memoria: parallelismo a 64 bit (esempio, bus del Pentium). Semplice estensione del caso a 32 bit.

Questa organizzazione della memoria consente di accedere in un solo ciclo a dati la cui dimensione va da 1 a 2<sup>K</sup> byte, purché questi siano allineati in memoria.