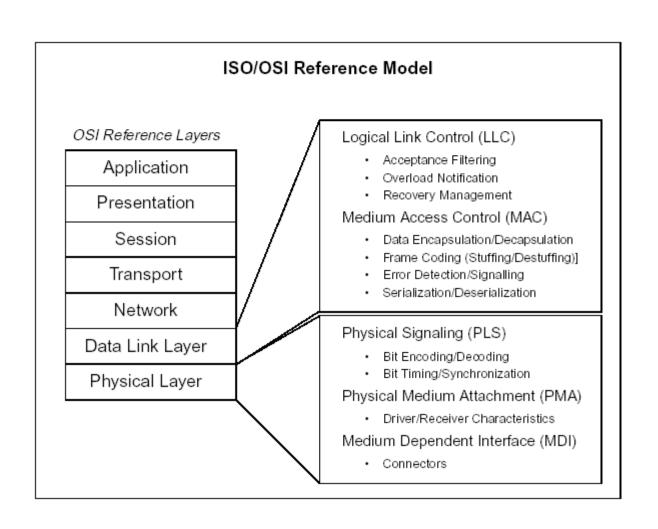

### Modello ISO-OSI e Livelli specificati dalla norma SAE J1939

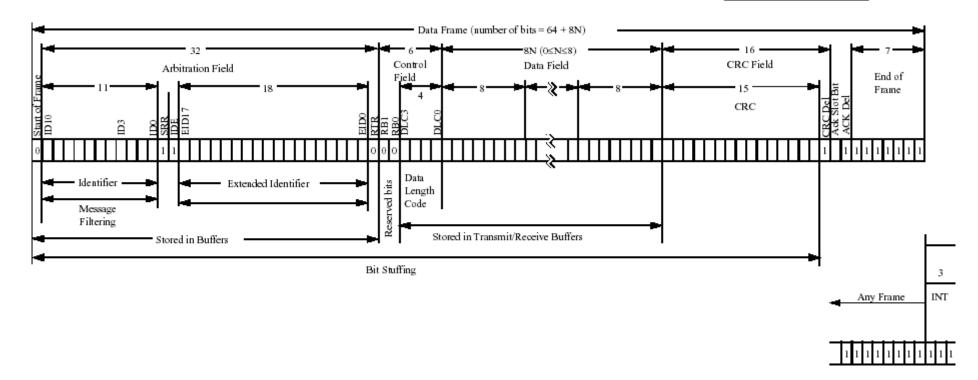

#### Struttura di un extended frame

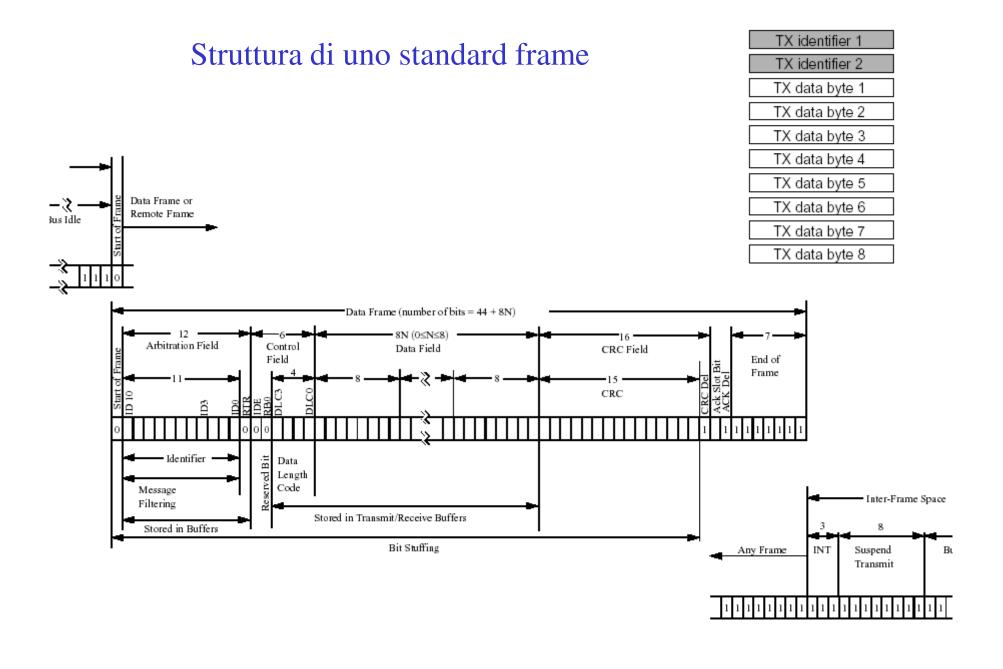

TX identifier 1

TX identifier 2

TX identifier 3

TX identifier 4

TX data byte 1

TX data byte 2

TX data byte 3

TX data byte 3

TX data byte 4

TX data byte 5

TX data byte 6

TX data byte 7

TX data byte 8

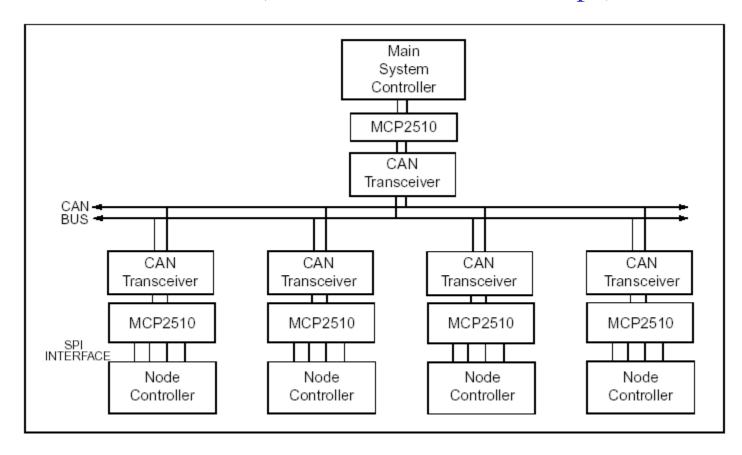

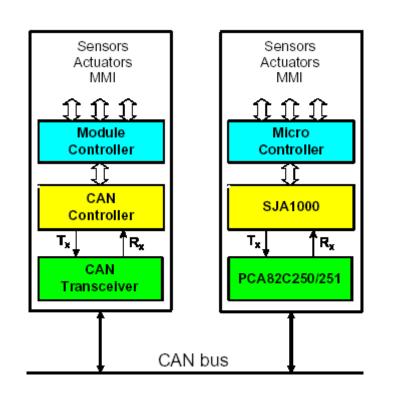

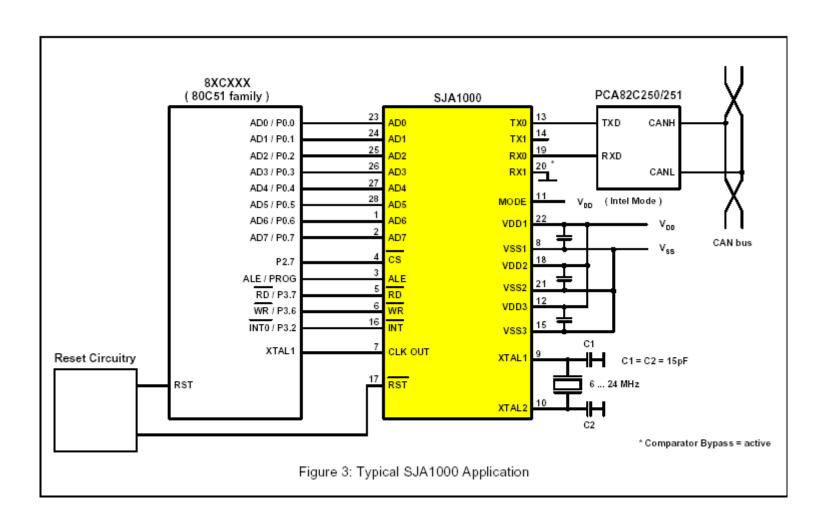

### Tipica implementazione di rete CAN singola

### Per ogni nodo è presente:

- un CAN controller (come SJA100 oppure MCP2510) e

- un CAN Transceiver (come PCA82C251 Philips)

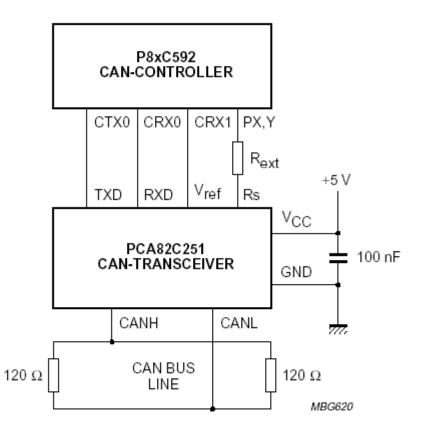

# Tipica implementazione di rete CAN singola: singolo nodo

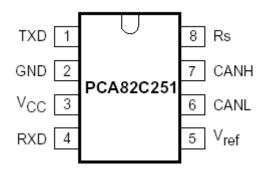

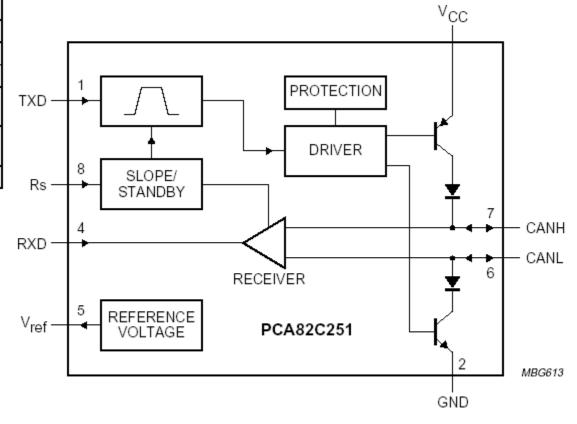

### Il CAN Transceiver PCA82C251 Philips:

Pinout e diagramma a blocchi interno

| SYMBOL    | PIN | DESCRIPTION                           |  |

|-----------|-----|---------------------------------------|--|

| TXD       | 1   | transmit data input                   |  |

| GND       | 2   | ground                                |  |

| Vcc       | 3   | supply voltage                        |  |

| RXD       | 4   | receive data output                   |  |

| $V_{ref}$ | 5   | reference voltage output              |  |

| CANL      | 6   | LOW level CAN voltage<br>input/output |  |

| CANH      | 7   | HIGH level CAN voltage input/output   |  |

| Rs        | 8   | slope resistor input                  |  |

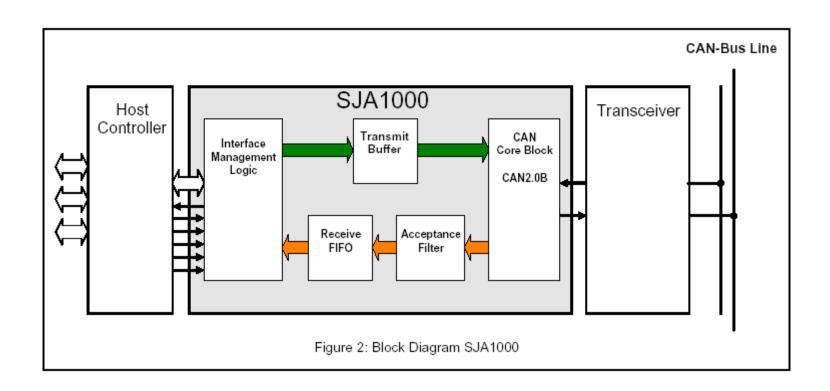

# Philips SJA1000 CAN Controller: Diagramma a Blocchi

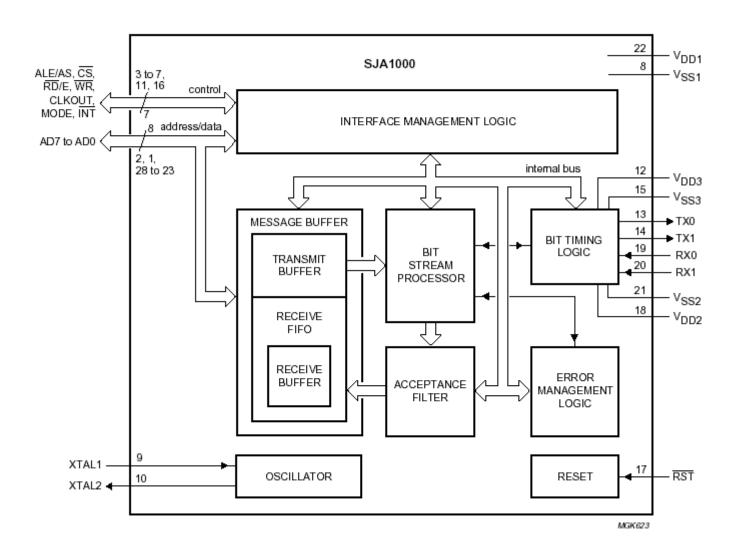

# Philips SJA1000 CAN Controller: Diagramma a Blocchi e pinout

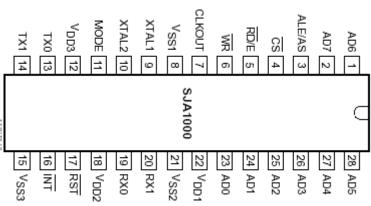

# Philips SJA1000 CAN Controller: Pinout

| SYMBOL           | PIN            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD7 to AD0       | 2, 1, 28 to 23 | multiplexed address/data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/AS           | 3              | ALE input signal (Intel mode), AS input signal (Motorola mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CS               | 4              | chip select input, LOW level allows access to the SJA1000                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD/E             | 5              | RD signal (Intel mode) or E enable signal (Motorola mode) from the microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WR               | 9              | WR signal (Intel mode) or RD/WR signal (Motorola mode) from the microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKOUT           | 7              | clock output signal produced by the SJA1000 for the microcontroller; the clock signal is derived from the built-in oscillator via the programmable divider; the clock                                                                                                                                                                                                                                                                                                                                               |

| Voca             | 00             | around for logic circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XTAL1            | 9              | input to the oscillator amplifier; external oscillator signal is input via this pin; note                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XTAL2            | 10             | output from the oscillator amplifier; the output must be left open-circuit when an external oscillator signal is used; note 1                                                                                                                                                                                                                                                                                                                                                                                       |

| MODE             | 11             | mode select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                | 1 = selects Intel mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  |                | 0 = selects Motorola mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD3             | 12             | 5 V supply for output driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TX0              | 13             | output from the CAN output driver 0 to the physical bus line                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TX1              | 14             | output from the CAN output driver 1 to the physical bus line                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS3</sub> | 15             | ground for output driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17               | 16             | interrupt output, used to interrupt the microcontroller; INT is active LOW if any bit of the internal interrupt register is set; INT is an open-drain output and is designed to be a wired-OR with other INT outputs within the system; a LOW level on this pin will reactivate the IC from sleep mode                                                                                                                                                                                                              |

| RST              | 17             | reset input, used to reset the CAN interface (active LOW); automatic power-on reset can be obtained by connecting RST via a capacitor to $V_{SS}$ and a resistor to $V_{DD}$ (e.g. $C = 1  \mu F$ ; $R = 50  k\Omega$ )                                                                                                                                                                                                                                                                                             |

| V <sub>DD2</sub> | 18             | 5 V supply for input comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RX0, RX1         | 19, 20         | input from the physical CAN-bus line to the input comparator of the SJA1000; a dominant level will wake up the SJA1000 if sleeping; a dominant level is read, if RX1 is higher than RX0 and vice versa for the recessive level; if the CBP bit (see Table 49) is set in the clock divider register, the CAN input comparator is bypassed to achieve lower internal delays if an external transceiver circuitry is connected to the SJA1000; in this case only RX0 is active; HIGH is interpreted as recessive level |

| Vss2             | 21             | ground for input comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vpp1             | 22             | 5 V supply for logic circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# SJA1000 e BIU (Bus Interface Unit) con µp della famiglia Intel a 8 bit con core 8088 (8051)

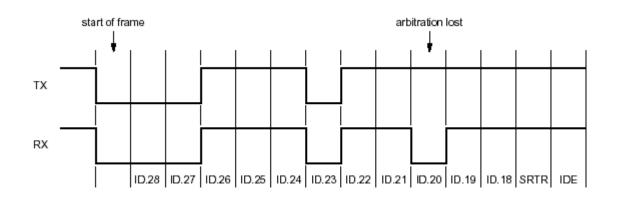

Arbitraggio durante la fase di emissione del Frame ID da parte di due diversi nodi della rete CAN (si suppone l'uso di Extended frames)

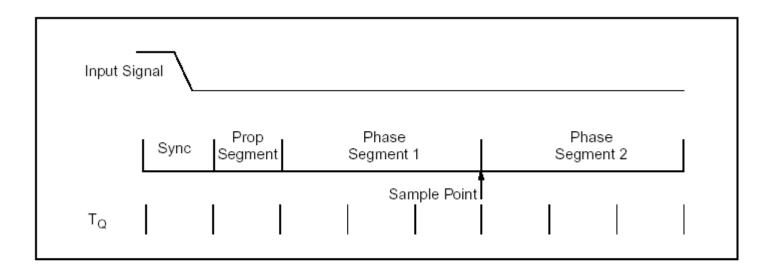

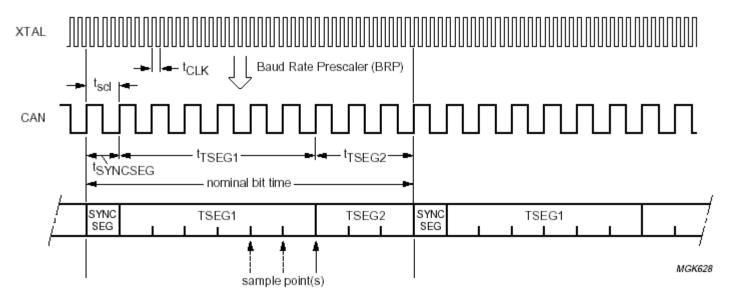

### Bit Time partitioning con evidenziazione del sample point

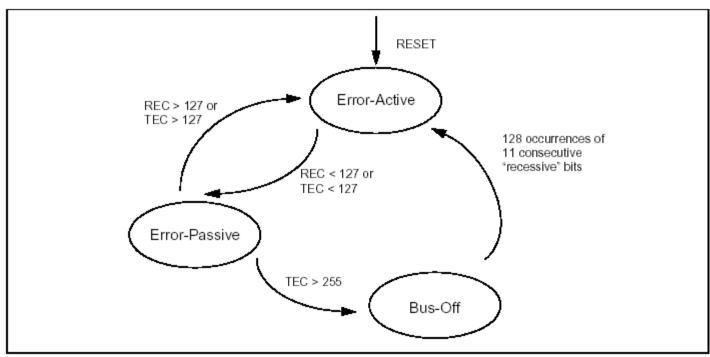

### Macchina a stati degli errori

Stati di:

TEC = Transmit Error Counter Error Active

REC = Receive Error Counter Error Passive

**Bus Off**

FIGURE 6-1: Error Modes State Diagram

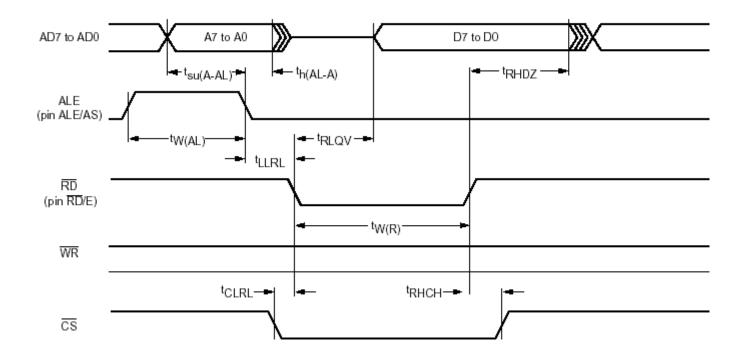

# Interfaccia verso la CPU e il Bus di sistema: Ciclo di lettura

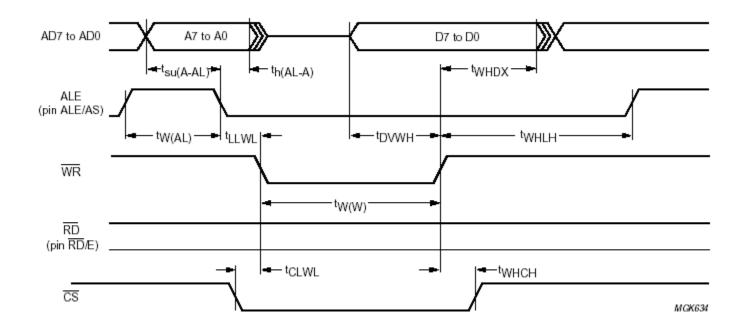

# Interfaccia verso la CPU e il Bus di sistema: Ciclo di scrittura

# Interfaccia verso la CPU e il Bus di sistema: Timing dei cicli di lettura e scrittura

| SYMBOL                | PARAMETER                     | CONDITIONS | MIN. | MAX. | UNIT |

|-----------------------|-------------------------------|------------|------|------|------|

| fosc                  | oscillator frequency          |            | _    | 24   | MHz  |

| t <sub>su(A-AL)</sub> | address set-up to ALE/AS LOW  |            | 8    | _    | ns   |

| t <sub>h(AL-A)</sub>  | address hold after ALE LOW    |            | 2    | _    | ns   |

| t <sub>W(AL)</sub>    | ALE/AS pulse width            |            | 8    | _    | ns   |

| t <sub>RLQV</sub>     | RD LOW to valid data output   | Intel mode | -    | 50   | ns   |

| t <sub>RHDZ</sub>     | data float after RD HIGH      | Intel mode | _    | 30   | ns   |

| t <sub>DVWH</sub>     | input data valid to WR HIGH   | Intel mode | 8    | _    | ns   |

| t <sub>WHDX</sub>     | input data hold after WR HIGH | Intel mode | 8    | _    | ns   |

| t <sub>whlh</sub>     | WR HIGH to next ALE HIGH      |            | 15   | _    | ns   |

| t <sub>LLWL</sub>     | ALE LOW to WR LOW             | Intel mode | 10   | _    | ns   |

| t <sub>LLRL</sub>     | ALE LOW to RD LOW             | Intel mode | 10   | -    | ns   |

| t <sub>W(W)</sub>     | WR pulse width                | Intel mode | 20   | _    | ns   |

| t <sub>W(R)</sub>     | RD pulse width                | Intel mode | 40   | _    | ns   |

| t <sub>CLWL</sub>     | CS LOW to WR LOW              | Intel mode | 0    | _    | ns   |

| t <sub>CLRL</sub>     | CS LOW to RD LOW              | Intel mode | 0    | _    | ns   |

| t <sub>WHCH</sub>     | WR HIGH to CS HIGH            | Intel mode | 0    | _    | ns   |

| t <sub>RHCH</sub>     | RD HIGH to CS HIGH            | Intel mode | 0    | _    | ns   |

| t <sub>W(RST)</sub>   | RST pulse width               |            | 100  | _    | ns   |